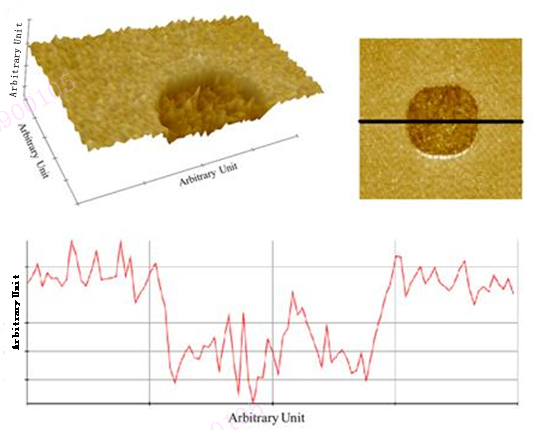

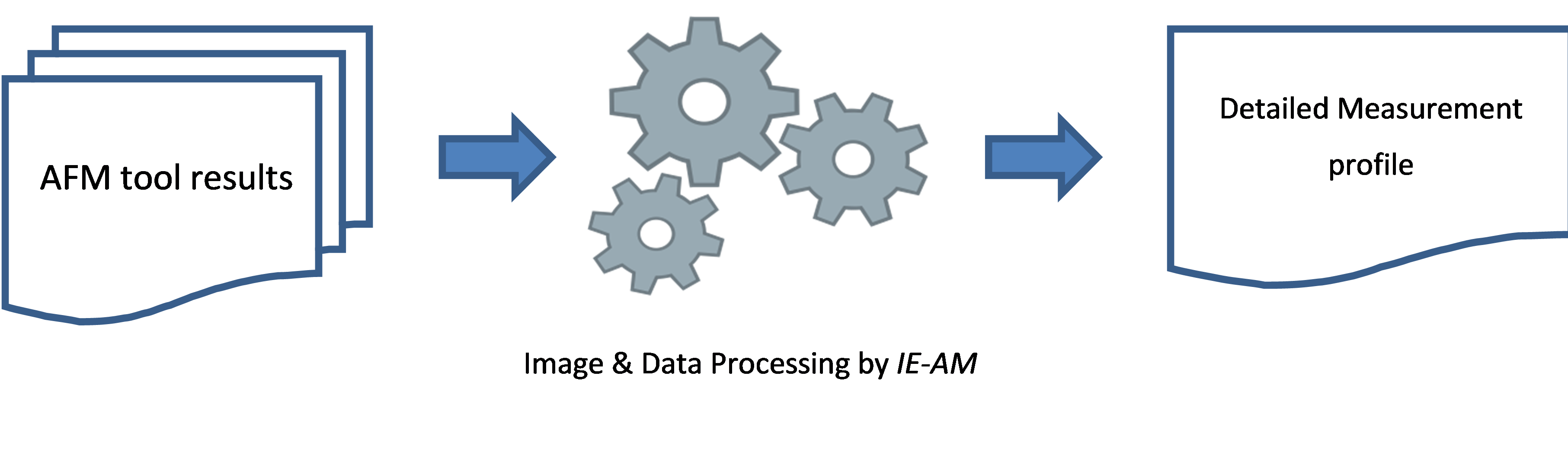

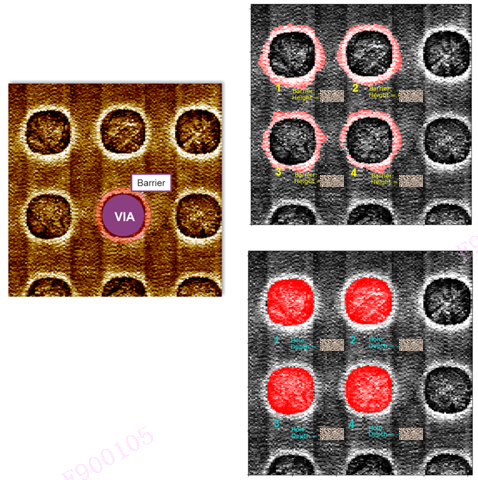

Abstract: 3D NAND (three-dimensional NAND type) has rapidly become the standard technology for enterprise flash memories, and is also gaining widespread use in other applications. Continued manufacturing process improvements are essential in delivering memory devices with higher I/O performance, higher bit density, and at lower cost. Current 3D NAND technology involves process steps that form array and peripheral CMOS (Complementary Metal-Oxide-Semiconductor) regions side-by-side, resulting in waste of silicon real estate and film stress compromises, and limits the paths of making advanced 3D NAND devices. An innovative architecture was invented to overcome these challenges by connecting two wafers electrically through metal VIAs (Vertical Interconnect Access) [1]. Highly accurate and efficient metrology is required to monitor VIA interface due to increased process complexity and precision requirements. With the advanced processing of AFM (Atomic Force Microscopy) images, highly accurate and precise measurements have been achieved. An inline pattern-centric metrology solution that is designed for high volume mass production of high-performance 3D NAND is presented in this paper.

Keywords: VIA; Dishing; AFM; Image; Metrology; 3D NAND