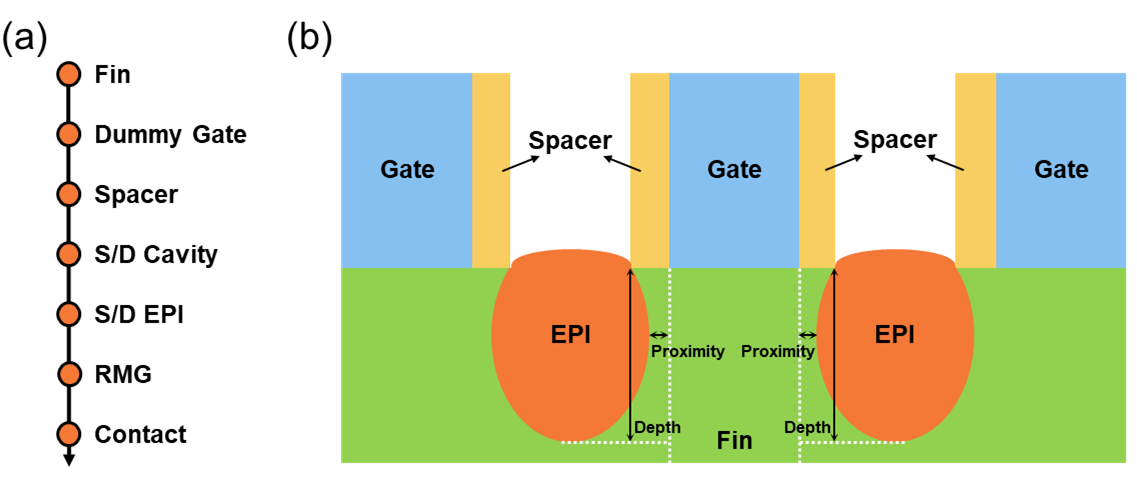

A fully integrated advanced bulk FinFET complementary metal-oxide semiconductor (CMOS) platform was adopted to perform this study. Figure 1(a) depicts the schematic process flow of advanced bulk FinFET fabrication [10]. After the formation of fin and dummy gate structures, low-dielectric constant (low-k) films were deposited over the wafer using an atomic layer deposition (ALD) process to form gate sidewall spacers [11, 12]. A reactive ion etching (RIE) process was then applied to form recessed cavity structures in the S/D regions for the subsequent epitaxy (EPI) processes. The S/D cavity formation process was comprised of three steps: removing the spacer from the top of the fin, recessing the exposed fin by an anisotropic etching process, and setting the final cavity geometry by an isotropic etching process. In the first step, the amount of the spacer pulldown on the fin is a critical parameter to control the lateral width of S/D EPI [13]. The second anisotropic etching step is the main step to recess the fin vertically along the gate sidewall spacer, and the third isotropic etching step is the final step to further etch the fin vertically and laterally under the spacer to achieve the desired cavity geometry. Figure 1(b) shows the typical cavity profile of a pFET device, the cavity depth is defined as the distance from the top of the fin to the bottom of the cavity, and the cavity proximity is defined as the distance from the lateral edge of the cavity to the edge of the gate. Following the cavity formation, S/D EPI processes were optimized according to the cavity geometry to achieve the desired EPI geometry, then the replacement metal gate (RMG) and metal contact formation processes were performed to complete FinFET fabrication. In this study, pFET devices with a range of cavity depth and proximity targets were fabricated by modifying the etching time of each individual step of the cavity formation process, in-situ boron (B) doped SiGe EPI was formed in the recessed cavity regions as the stressor to enhance the hole mobility [14–17]. The impact of applying a low-energy B ion implantation process in the S/D cavity regions before SiGe EPI formation was also investigated.

Figure 1.

(a) Schematic process flow of advanced bulk FinFET fabrication. (b) Schematic pFET device structure along the fin, the S/D cavity depth and proximity are also shown.