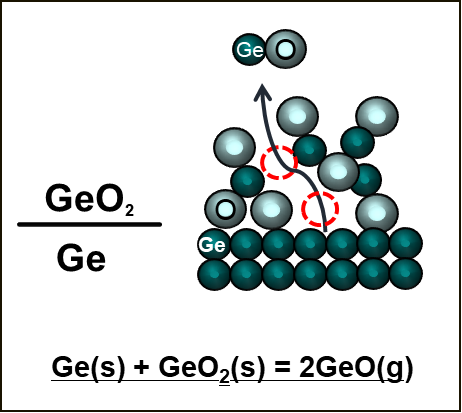

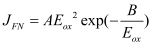

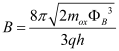

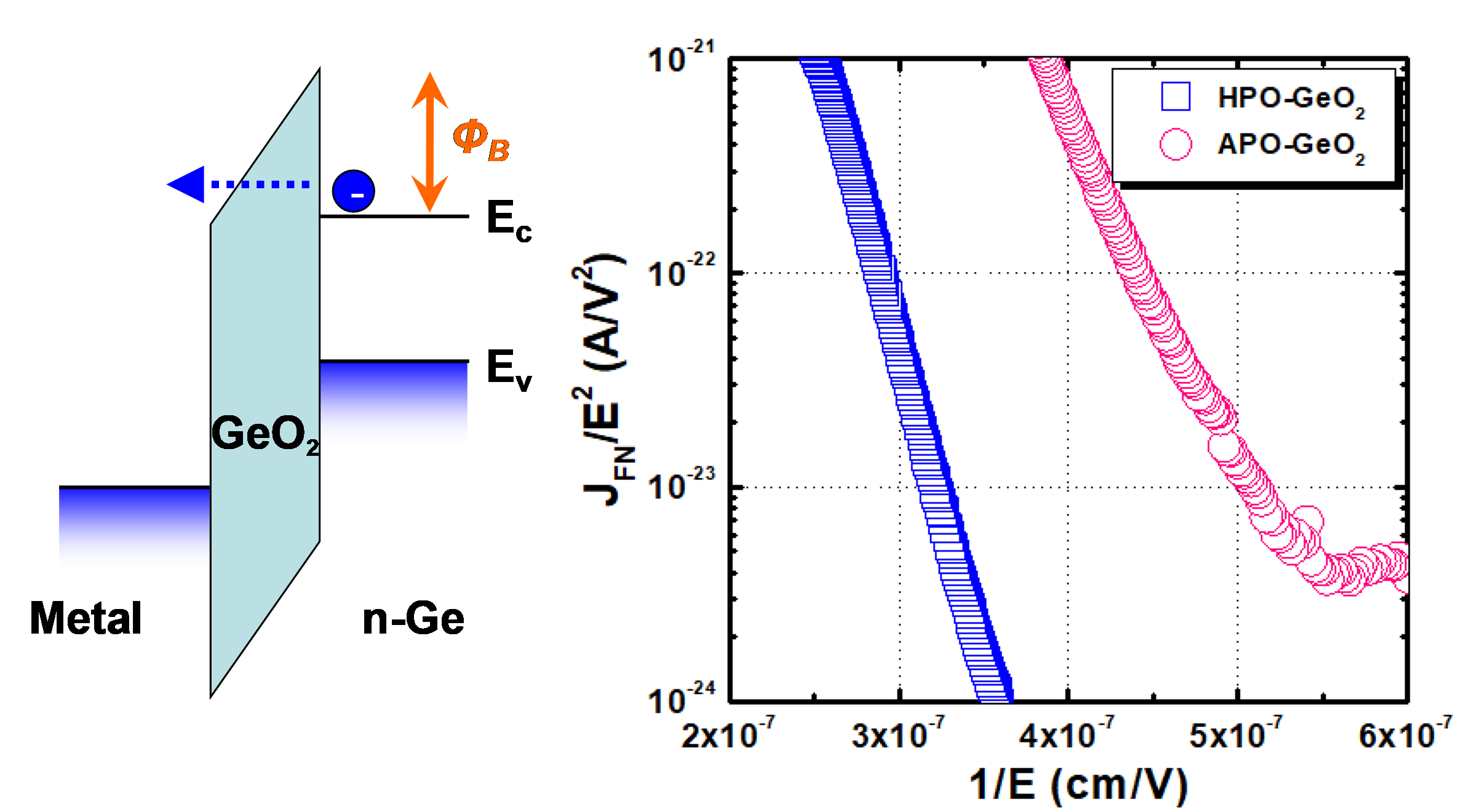

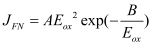

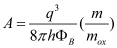

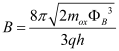

In order to investigate the GeO2 bulk properties in the Ge/GeO2 stack, the same thickness of GeO2 film was thermally grown on Ge (100) wafers by APO and HPO, respectively. For the interface passivation of Ge/GeO2 stacks, the post oxidation annealing at 400oC for 60 min was carried out for both HPO-grown and APO-grown Ge/GeO2 stacks. Since Ge/GeO2 interface properties are superior enough and similar to both HPO-grown and APO-grown Ge/GeO2 stacks with the post oxidation annealing, the influence of Ge/GeO2 interface properties can be excluded from the discussion of GeO2 bulk properties. The conduction band offset (ΦB) is one of the most important factors as the gate insulator to suppress the gate leakage current. In order to extract and compare the ΦB between GeO2 and Ge substrate, both n-type MOSCAPs with APO-grown GeO2 and HPO-grown GeO2 are investigated. Figure 5(a) shows a plot of ln(JFN/E2) versus (1/E), where JFN is the current density and E is the electric field of GeO2, known as the Fowler-Nordheim (F-N) plot. The F-N tunneling current density JFN can be expressed as follows [18]:

,

where

and

. Here,

h is the Planck constant,

q is the electron charge,

Eox is the electric field in the GeO

2, Φ

B is the barrier height,

m is the free electron mass, and

mox is the effective electron mass in the GeO

2. Since

mox is an unknown factor,

mox is assumed to be 0.42

m, which is generally accepted as the effective electron mass in the SiO

2. If the F-N plot is linear, the intercept of this F-N plot gives

A and the slope yields

B. The calculated Φ

B from above equations is 1.5 eV for HPO-grown GeO

2 on Ge and 1.2 eV for APO-grown GeO

2 on Ge, respectively. The value of Φ

B for Ge/GeO

2 stack with APO is well consistent with other report

[19], where GeO

2 was thermally oxidized at 550

oC in 1-atm O

2 ambient. Figure 5(b) shows the calculated Φ

B from F-N plot as a function of

mox . It is expected that the Φ

B from Ge/GeO

2 stack grown by HPO is about 0.3 eV higher than that of Ge/GeO

2 stack grown by APO, regardless of

mox . This difference of Φ

B in the Ge/GeO

2 stacks might be originated from bulk defects in the GeO

2 film, which is generated by GeO desorption during the conventional thermal oxidation.

Figure 5.

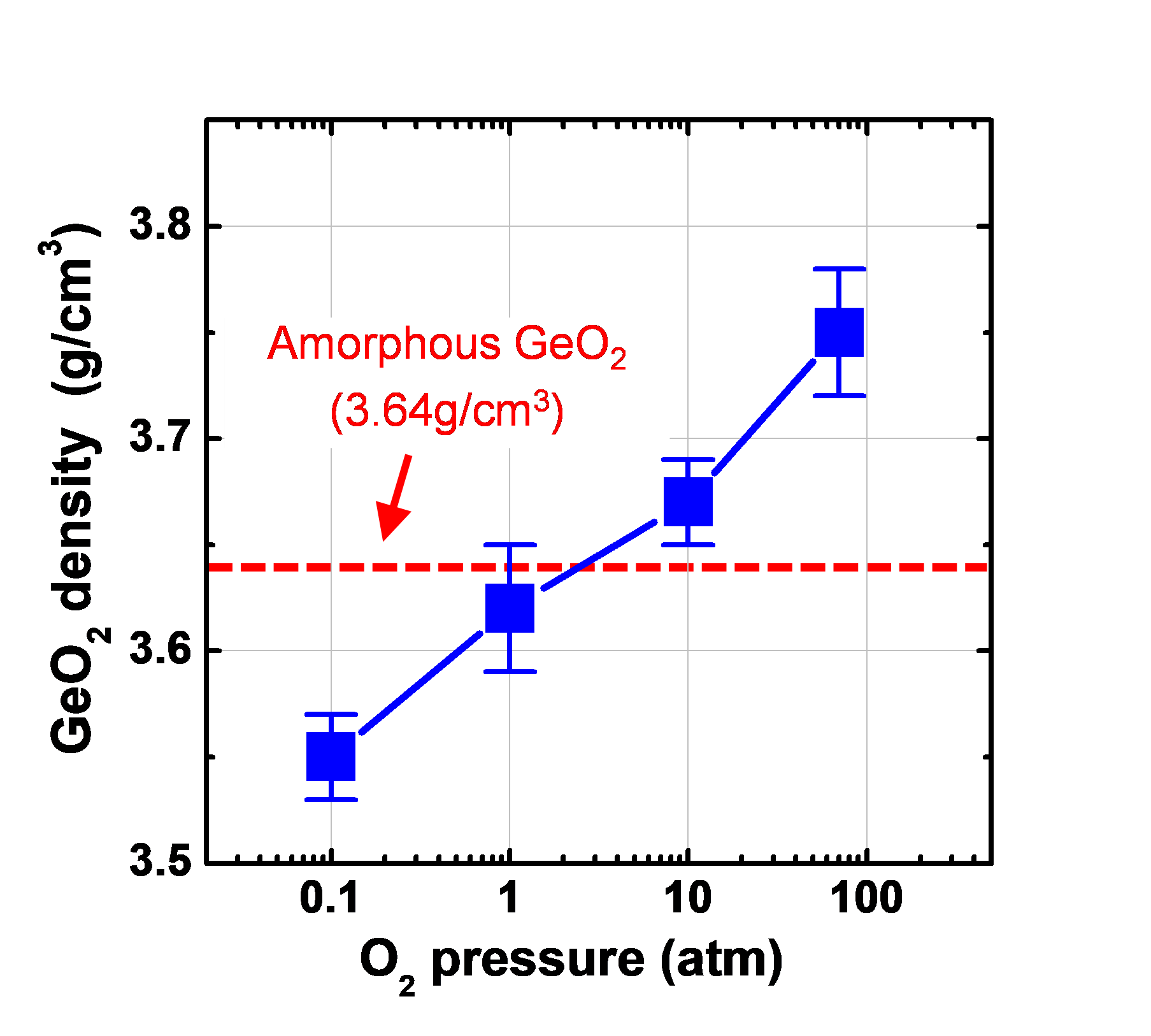

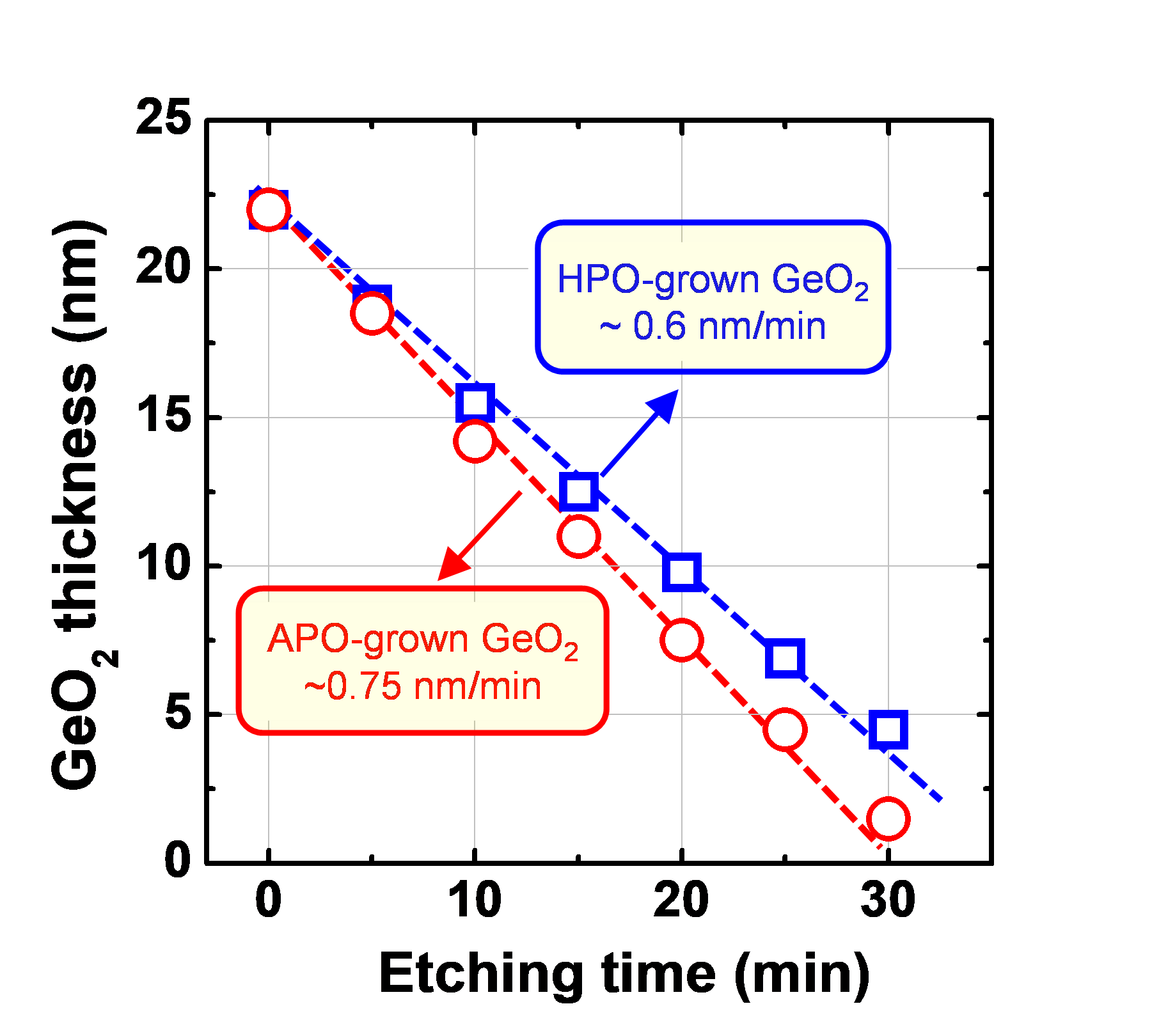

(a) Fowler-Nordheim (F-N) plot for HPO-grown and APO-grown GeO2 on Ge samples, where the thickness of both HPO-grown and APO-grown GeO2 film is 25 nm. Under the assumption that the effective electron mass in the GeO2 is 0.42m, the calculated conduction band offset is 1.5 eV for HPO-grown GeO2 and 1.2 eV for APO-grown GeO2, respectively. (b) Calculated conduction band offset between GeO2 and Ge as a function of effective electron mass in the GeO2. It is expected that the ΦB from Ge/GeO2 stack grown by HPO is about 0.3 eV higher than that of Ge/GeO2 stack grown by APO, regardless of mox . To further investigate the GeO2 bulk properties, the GeO2 film density was estimated by grazing incidence X-ray reflectometry. Figure 6(a) shows the GeO2 film density as a function of PO2 in the thermal oxidation. It clearly shows that GeO2 film density increases with the increase of PO2. For comparison, the density of amorphous GeO2 film is included [20], which is in good agreement with APO-grown GeO2 film. It is well known that there is a strong correlation between dielectric film density and their wet etch rate. Since GeO2 is water soluble and readily dissolved in deionized water, we prepared the dilute deionized water solution (C2H5OH + H2O) to study the wet etch rate of GeO2 films grown by APO and HPO, respectively. Figure 6(b) shows the wet etch rate of GeO2 film in dilute deionized water solution. As expected from the film density, HPO-grown GeO2 film shows the slower wet etch rate (~0.6 nm/min) than APO-grown GeO2 film (~0.75 nm/min).

Figure 6.

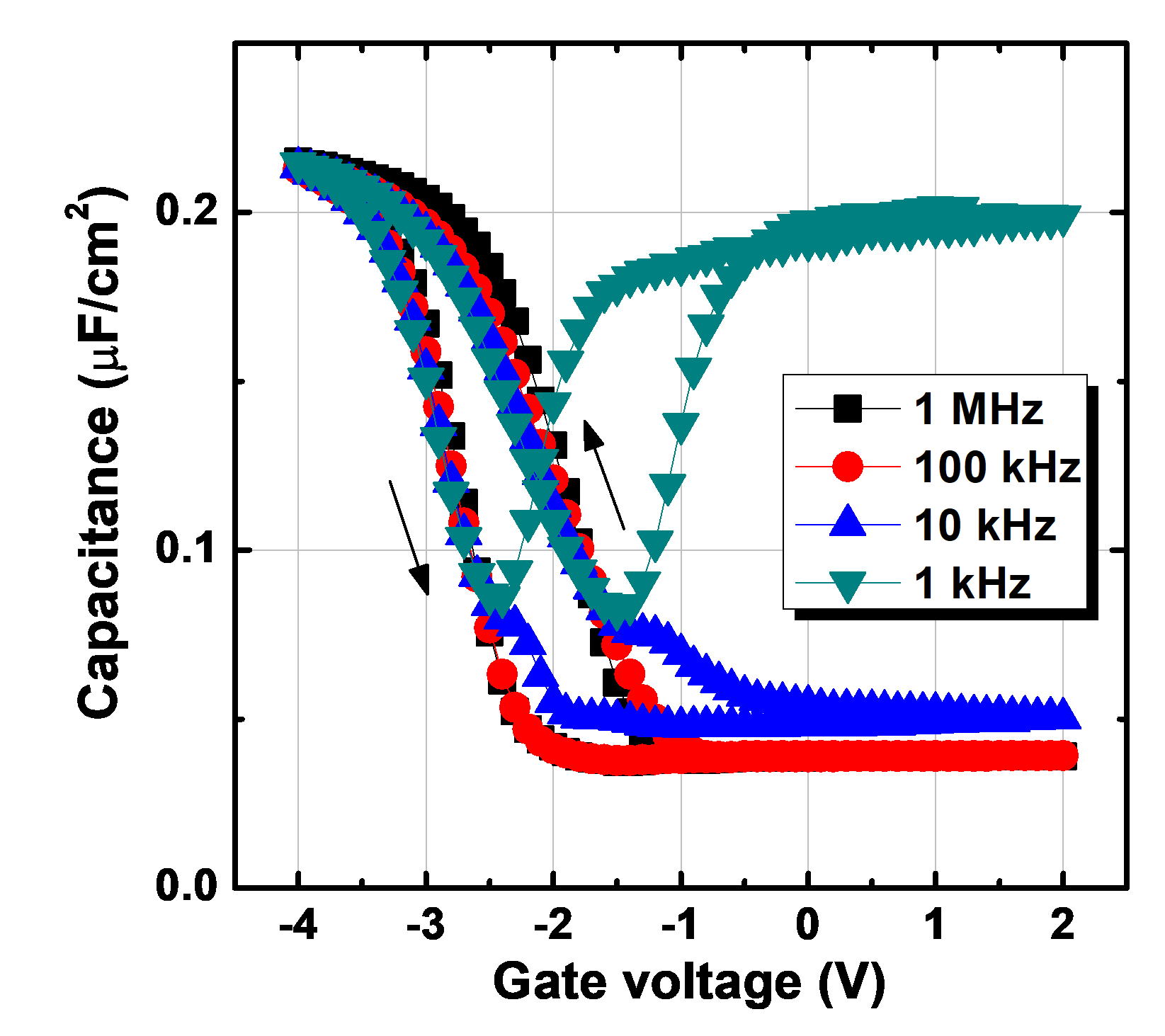

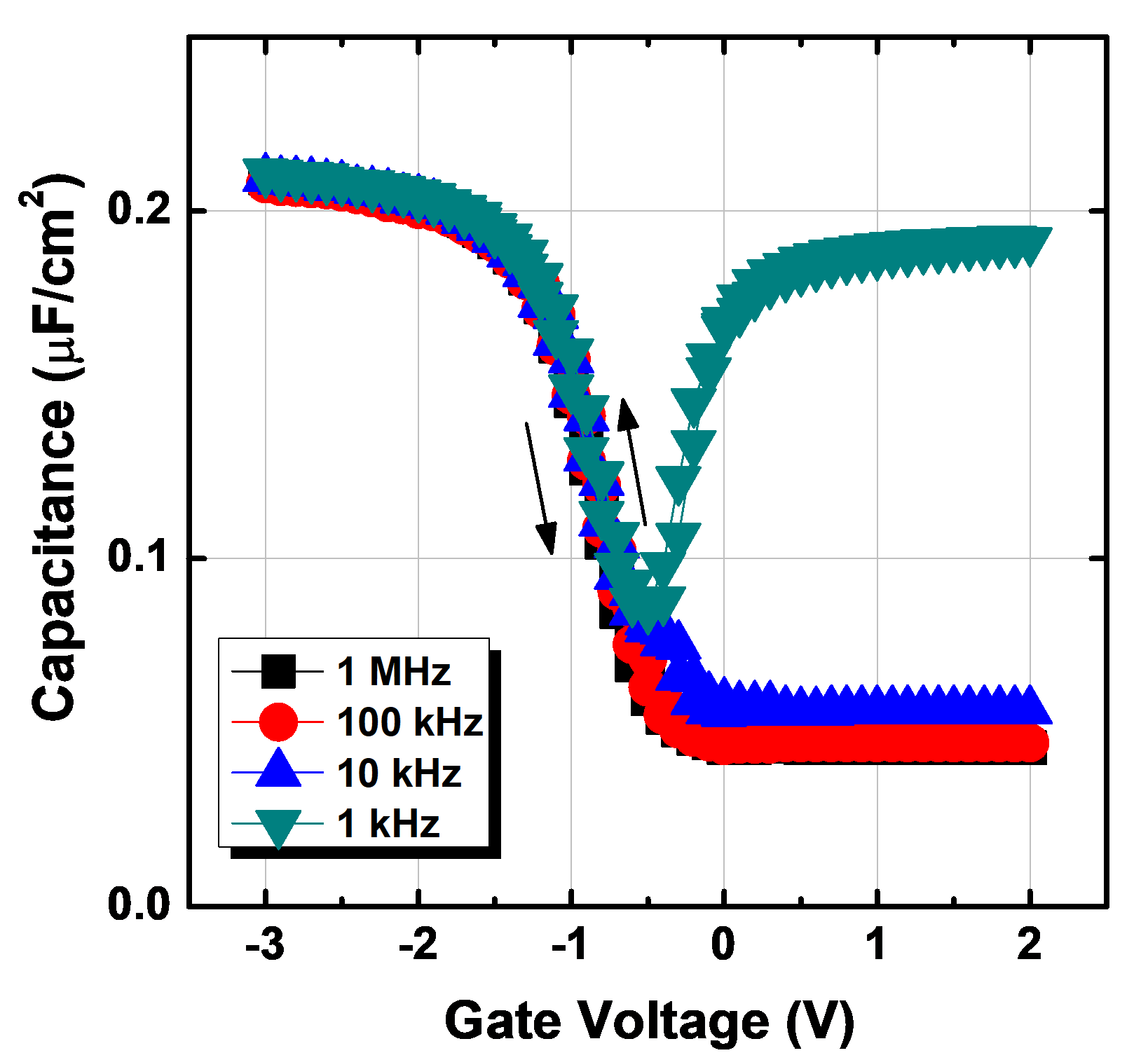

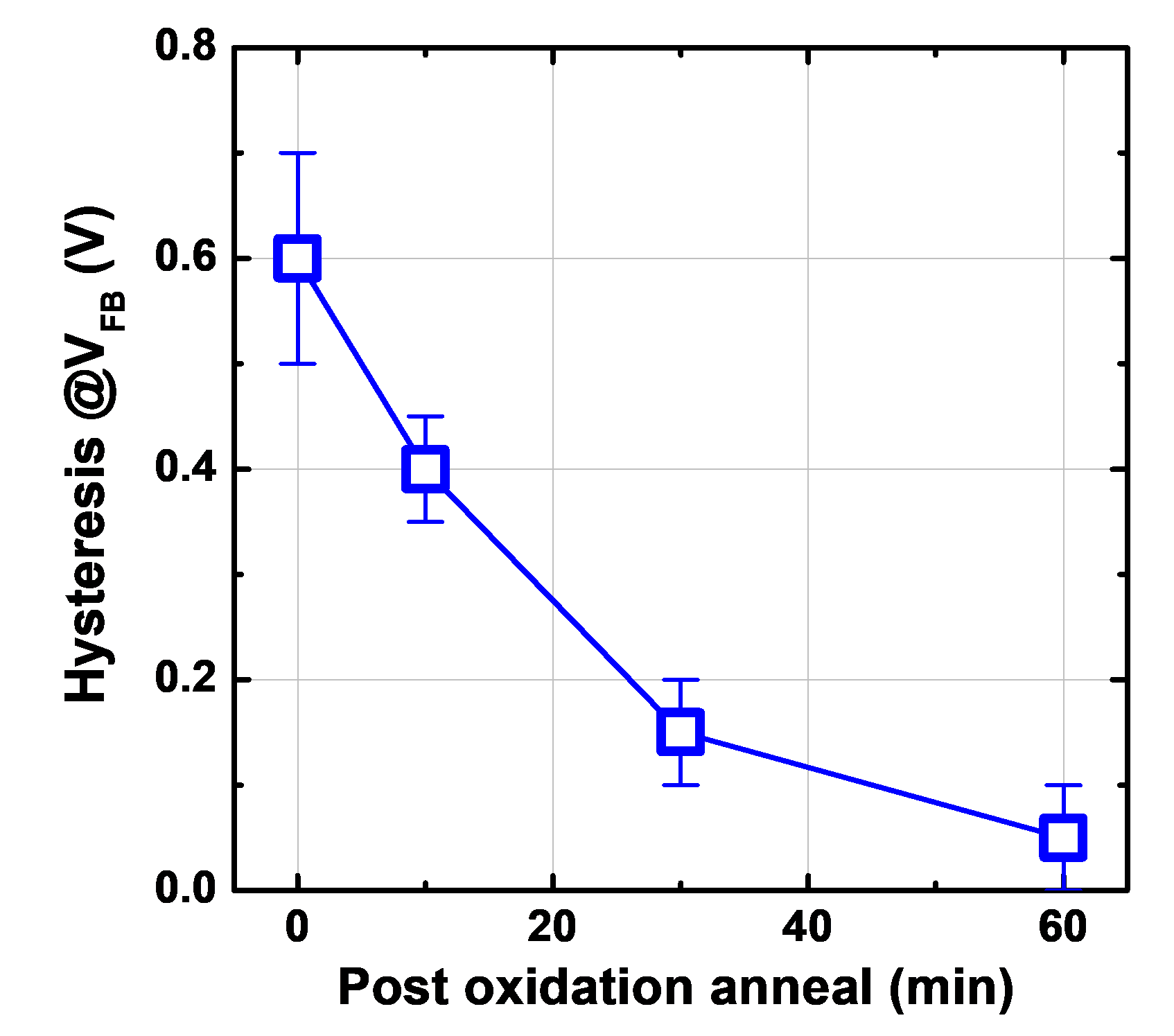

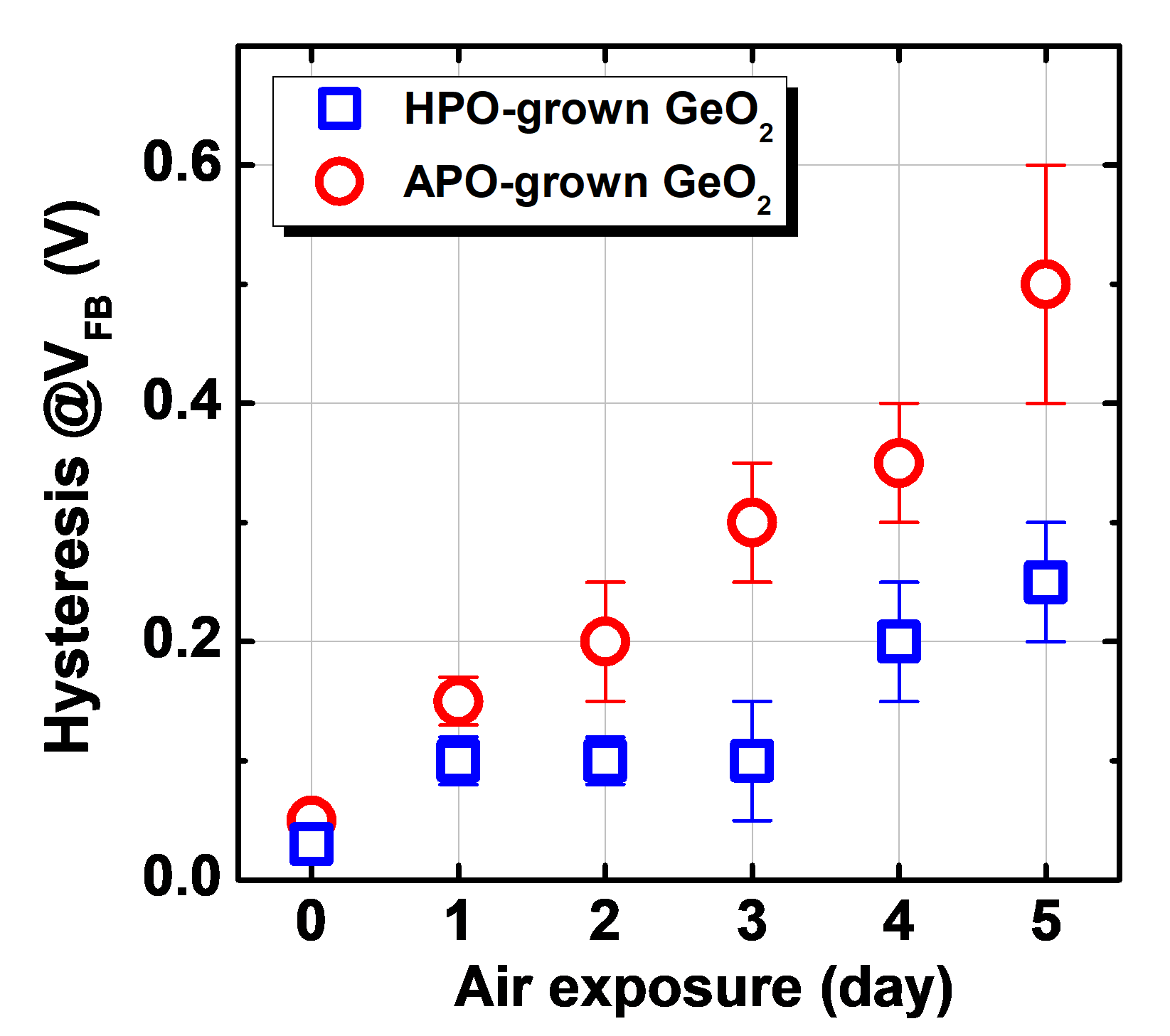

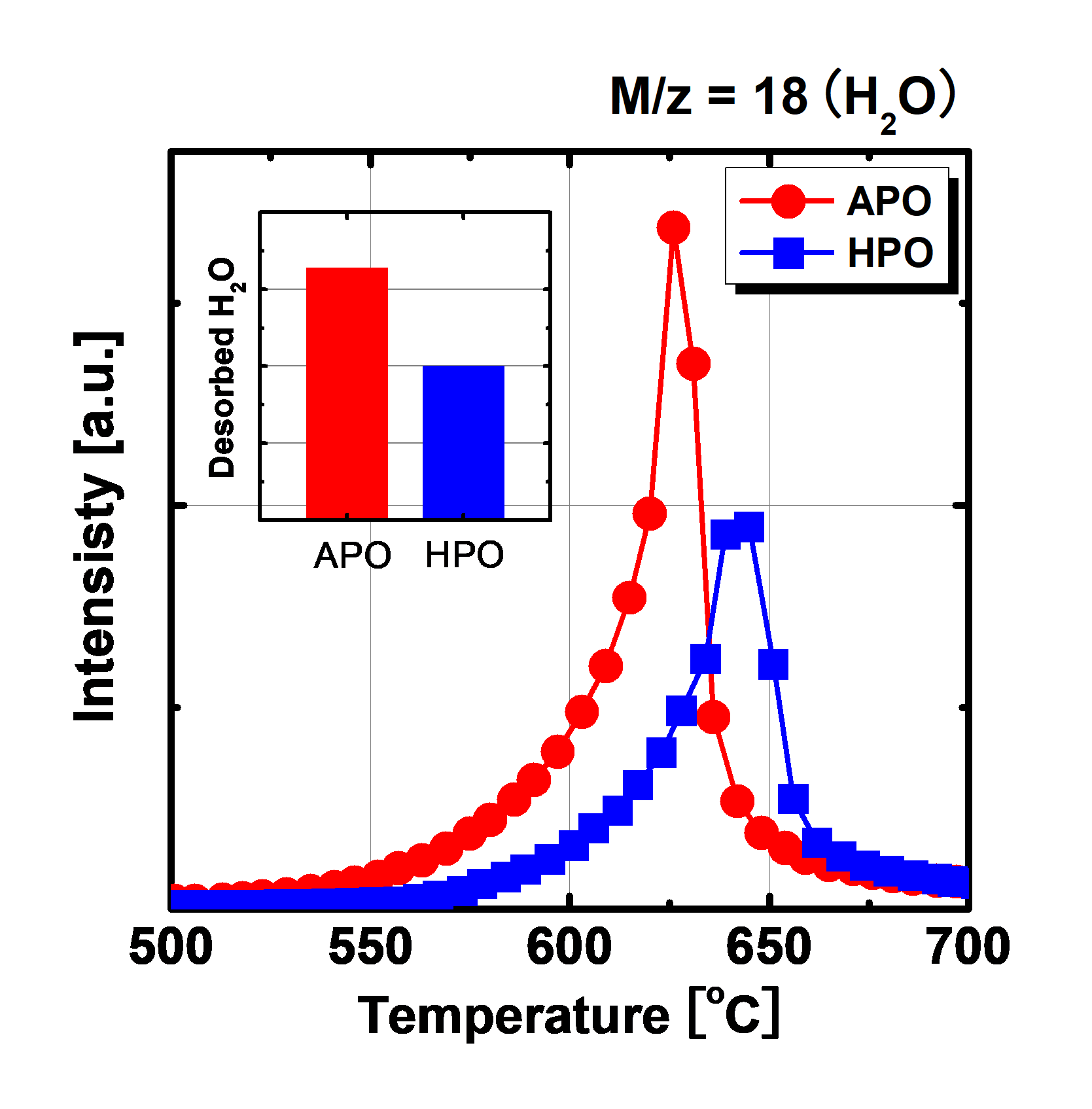

(a) GeO2 film density estimated by grazing incidence X-ray reflectometry as a function of O2 pressure in the thermal oxidation. It clearly shows that GeO2 film density increases with the increase of PO2. (b) Wet etch rate of GeO2 in the dilute deionized water solution. HPO-grown GeO2 film shows the slower wet etch rate than APO-grown one, which is good agreement with PO2 dependence of GeO2 film density. Since GeO2 film is easily etched in water, a strong influence of moisture absorption in the air on Ge/GeO2 stack is expected. Figure 7(a) shows the hysteresis of C-V characteristics extracted at flat-band voltage as a function of the air exposure time, where Ge/GeO2 stacks were exposed to the air before the gate electrode formation. A clear difference of electrical degradation rate between HPO-grown Ge/GeO2 stack and APO-grown Ge/GeO2 stack against the air exposure is observed. The effects of air exposure on electrical properties in Ge/GeO2 stack in terms of water absorption and hydrocarbons are comprehensively discussed in the literature [21], which is well consistent with our results. After 5-day air exposure, the desorbed H2O was measured by thermal desorption spectroscopy, as shown in Figure 7(b). It shows that APO-grown GeO2 film has about 40% more H2O molecules than HPO-grown one, indicating that HPO-grown GeO2 film has a higher hygroscopic tolerance. From the results of GeO2 bulk properties, it is concluded that one of the primary advantages of HPO on Ge is the improvement of GeO2 bulk properties by suppressing GeO desorption and accelerating the oxidation process at high temperatures. Dangling bonds at the Ge/GeO2 interface can be effectively passivated by post oxidation annealing at low temperature, while robust GeO2 bulk properties can only be achieved by HPO. The optimization of HPO and post oxidation annealing, which can further improve both GeO2 bulk and Ge/GeO2 interface properties, will be the most suitable for the formation of high-quality Ge/GeO2 stack.

Figure 7.

(a) Hysteresis of C-V characteristics as a function of air exposure time, where Ge/GeO2 stacks were exposed to air before the gate electrode formation. (b) Comparison of desorbed H2O in HPO-grown and APO-grown GeO2 films after 5-day air exposure. Thermal desorption spectroscopy is used to measured H2O molecules desorbing from GeO2 film. It shows that APO-grown GeO2 film has about 40% more H2O molecules than HPO-grown one, indicating that HPO-grown GeO2 film has a higher hygroscopic tolerance.