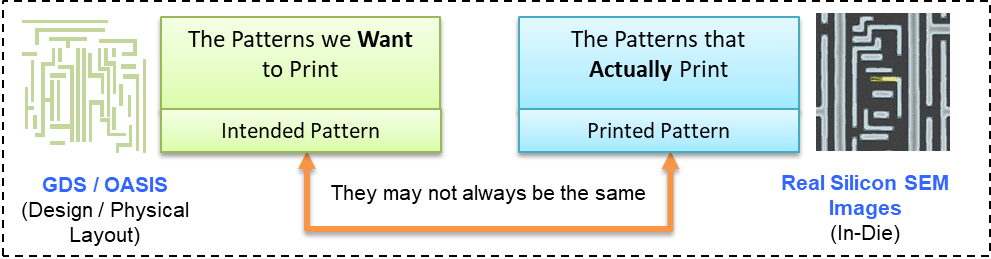

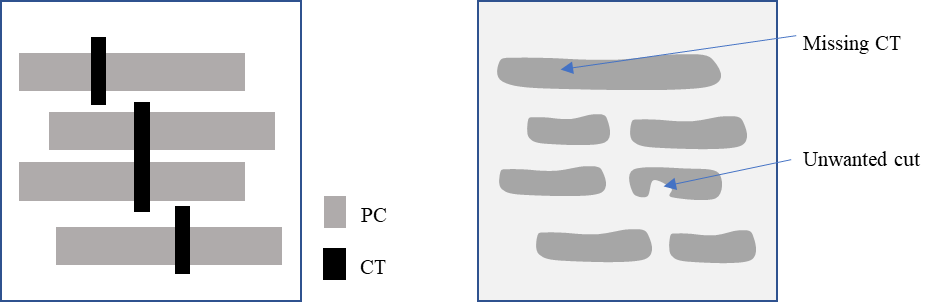

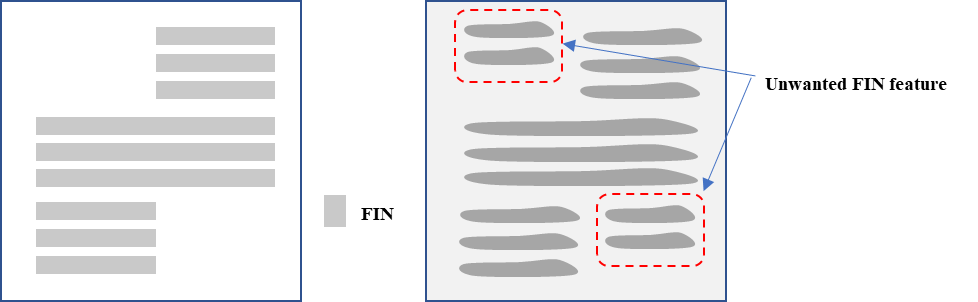

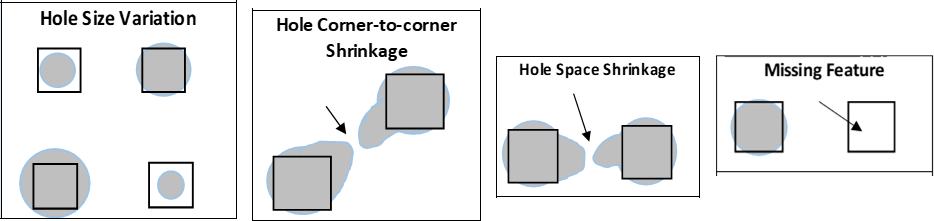

Pattern

fidelity – not just

defectivity – has always been of importance to the fab, but fidelity monitoring has been limited to low-frequency, time-consuming CD-SEM (Critical Dimension Scanning Electron Microscope) measurements

[9,10]. CD-SEMs continue to play an important role in accurately measuring features from both orthogonal and oblique angles. These measurements are typically performed on preselected features on designated wafers.

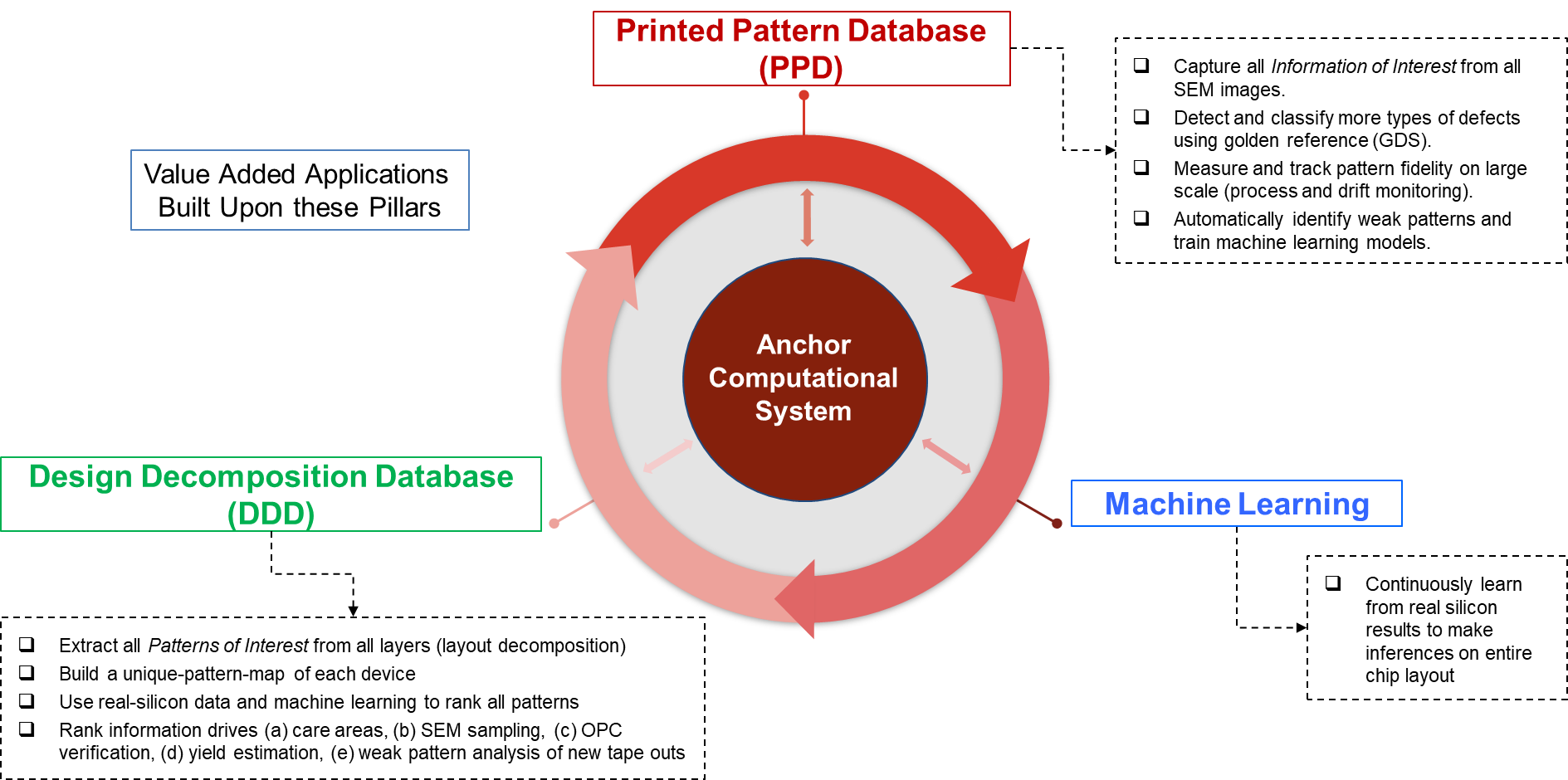

Anchor’s computational system reimagines the concept and deploys it on a massive scale on all wafers and on all features for which there are Review SEM images. The line itself is monitored not only for the traditional concept of

defect, but also for the concept of

pattern fidelity, which is in effect a “CD”-type measurement, but without the same level of measurement accuracy as a calibrated CD-SEM measurement. As such, inline continuous massive pattern fidelity measurement supplements the conventional CD-SEM operation

[11]. It has the potential to provide much earlier warnings of pending problems by tracking changes or trends in pattern fidelity

before they become bona fide defects. At the leading technology nodes, even small changes in pattern fidelity lead to significant electrical parasitics or parametric issues. A

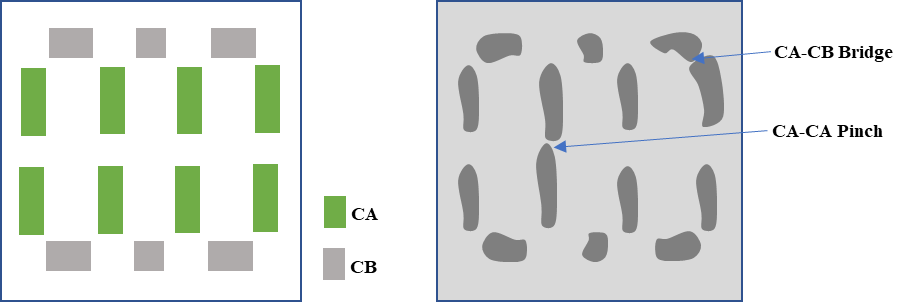

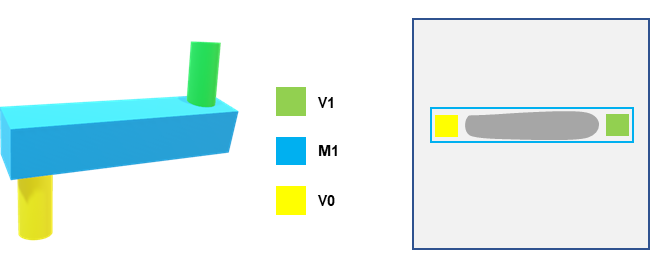

resistive via, for instance, may be caused by a slightly narrow and therefore partially blocked via that can impact device timing characteristics, produce single bit failures in memory devices, and produce various other parametric problems. Line thinning, line edge roughness, corner rounding, corner-to-corner artifacts, etc. are all liable to cause parametric issues.

Anchor’s computational system performs massive pattern fidelity analysis on each image, but does so in a pattern-centric manner that searches each aligned SEM image for all patterns of interest or POI, measures their printed dimensions, compares them against the reference design, and stores all results in the Printed Pattern Database.

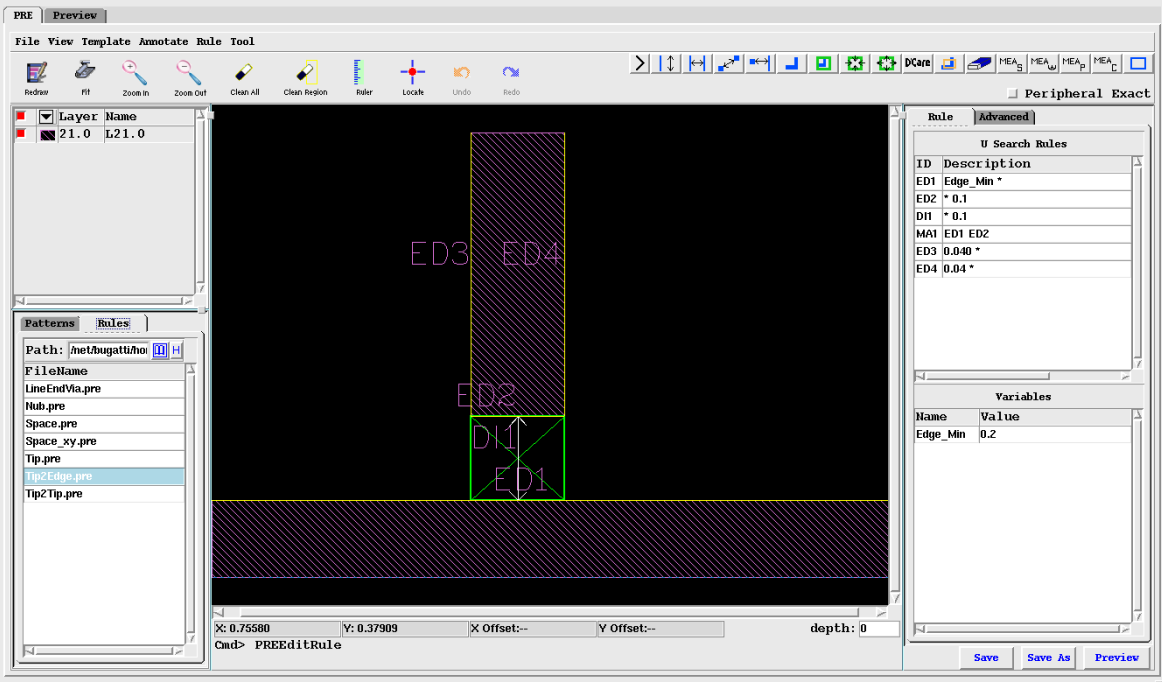

Patterns-of-interest (POI) are based on one or more parametric search rules. POI can also be identified automatically from the Design Decomposition Database by searching for patterns with high risk scores. Here we provide an example based on parametric search. Tip-to-line is a common pattern-of-interest, in which the amount of gap between tip and line (among other parameters) may affect printability or pattern fidelity.

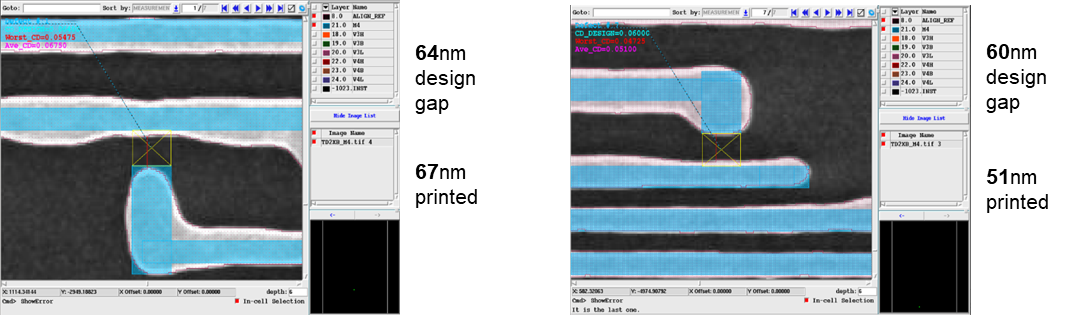

In the example shown in Figure 11, we use a graphical user interface (GUI) to create a tip-to-line rule. We specify several constraints such as the maximum width of the tip, the minimum length of the tip, and the maximum gap between tip and line. We want the rule to match tips whose widths are less than 100nm, whose lengths are at least 40nm, and the gap is at most 100nm.

Figure 11.

Defining Tip-to-Line Rule with Parameters (Constraints). This single rule will match all variations of tip-to-line where the tip width is less than 100nm, the tip length is greater than 40nm, and the gap is less than 100nm. When we run this rule against the two sample SEM images shown in Figure 12, we find a match where the reference tip-to-line gap (from design) is 64nm and another where the reference gap is 60nm. Once these patterns of interest (in blue) have been found, their printed sizes are measured either (a) from the image itself or (b) from the extracted contour. In the first example, the measured value is 67nm, and in the second, the measured value is 51nm.

Figure 12.

Two variations of tip-to-line matched by the parametric search rule. Because each SEM image is scanned from top to bottom, there might be tens or hundreds of matching patterns on each image. From a small set of sample images, we obtained the result as shown in Figure 13.

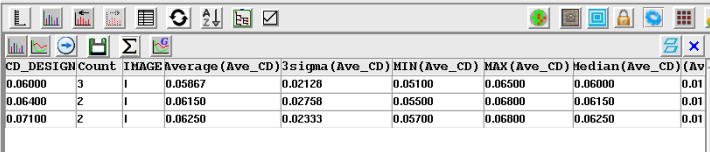

Figure 13.

Sample measurement results of tip-to-line. In column 1 we see that the tip-to-line rule found 3 variations of the pattern:

Variation 1: Reference gap 60nm. Average of the printed gap was 58.67nm

Variation 2: Reference gap 64nm. Average of the printed gap was 61.50nm

Variation 3: Reference gap 71nm. Average of the printed gap was 62.50nm

Litho/OPC and process engineers can examine this table to study the effects of gap size on the overall fidelity of the printed pattern. They can ask questions such as if the design or reference gap is reduced to X, how will that affect the printability of the pattern? Similarly, if the design or reference gap is enlarged to Y, how will that affect the printability of the pattern? In other words, the effects of specific variations in the physical layout can be studied in a comprehensive manner.

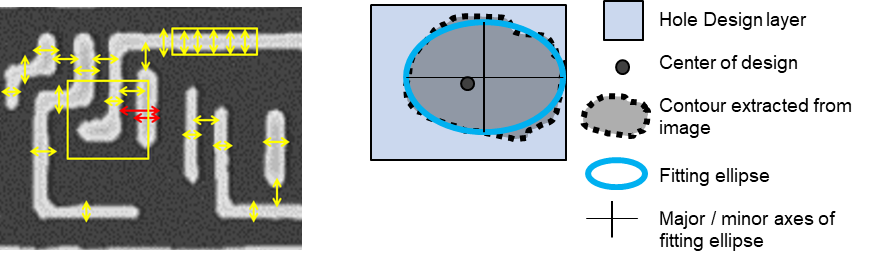

This example also demonstrates the value of speaking the universal language of patterns. There are more examples shown in Figure 14 that demonstrate the potential of SEM images to reveal detailed analysis of process variation. Anchor’s computation system is like an “analog to digital” converter – it converts the rich information content of analog SEM images into concise digital design patterns while retaining all of the information associated with the analog print.

When we expand the example by using (a) multiple parametric search rules and (b) hundreds or thousands of SEM images, we obtain a deep understanding of the process and its limitations. For (a) each pattern type (e.g. tip-to-line, tip-to-tip, etc.) and (b) each variation of each pattern type (e.g. tip-to-line gaps of 60nm, 64nm, 71nm, etc.) we create a Box Plot that represents all of the measurements of that particular pattern variation. For instance, if we found and measured fifty tip-to-line patterns with intended gap of 60nm, we create a box plot that shows how close or how wide apart all of the individual measurements were, and how much those measurements deviated from the reference of 60nm.

Figure 14.

Additional examples of various features being measured. If we do the same for all patterns and their variations, we end up with a box plot as shown below. Each box represents the measurements of one specific pattern (e.g. tip-to-line with reference gap of 60nm). In this example we see numerous patterns.

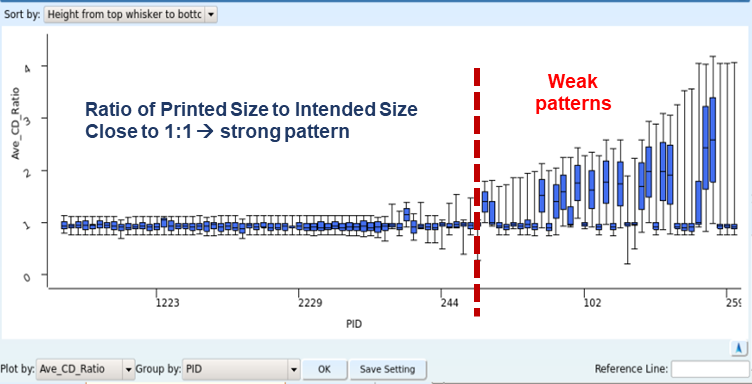

Figure 15.

Box Plot of Various Patterns as a Function of the Ratio of Printed Pattern Measurement to Intended Pattern Measurement. Values closer to 1:1 indicate strong patterns. Each box in a box plot shows several statistics about each specific pattern: the average and median values of all measurements, the range where most of the values are clustered, and outliers. It is a particularly effective way to identify weak and strong patterns, as shown in Figure 15. This particular box plot is based on the ratio of measured value to intended value. If the ratio is 1:1, it indicates a strong pattern because the measured values of all instances of that pattern matched the intended value. The more a box diverges from 1:1, the weaker the pattern. In this chart we see that the left half of patterns are printing well, with ratios close to 1, but the right half diverges significantly, indicating progressively weaker patterns. This automatically separates weak patterns from strong patterns, providing actionable information for root cause analysis.

Although this chart shows a large collection of patterns, we can track the behavior of individual patterns as well. Given a particular pattern A, we can:

Build a box plot of its measurements by time and track the fidelity of pattern A day-by-day or week-by-week or before-and-after a mask or process revision.

Build a box plot of its measurements sorted by process tool ID (e.g. scanner 1 or scanner 2, or etcher 1 or etcher 2, or chamber 1 or chamber 2) for (a) tool matching purposes, (b) identification of problematic tool or chamber, or (c) process drift monitoring.

Build a box plot of its measurements by Focus / Exposure modulation on an PWQ or FEM wafer to study the subtle changes in the behavior of pattern A across F/E modulations. (See next section.)

4.6. Innovative FEM/PWQ Analysis and Process Window Determination

Lithography process window determination is a critical step in the setup and tuning of a scanner recipe. Two of the most significant recipe parameters are (a) focus offset and (b) exposure dose. Different patterns and different neighborhoods of those patterns are affected differently by focus and exposure settings, which are determined by exposing a reticle or mask using a series of focus and exposure modulations and analyzing the results of each modulation.

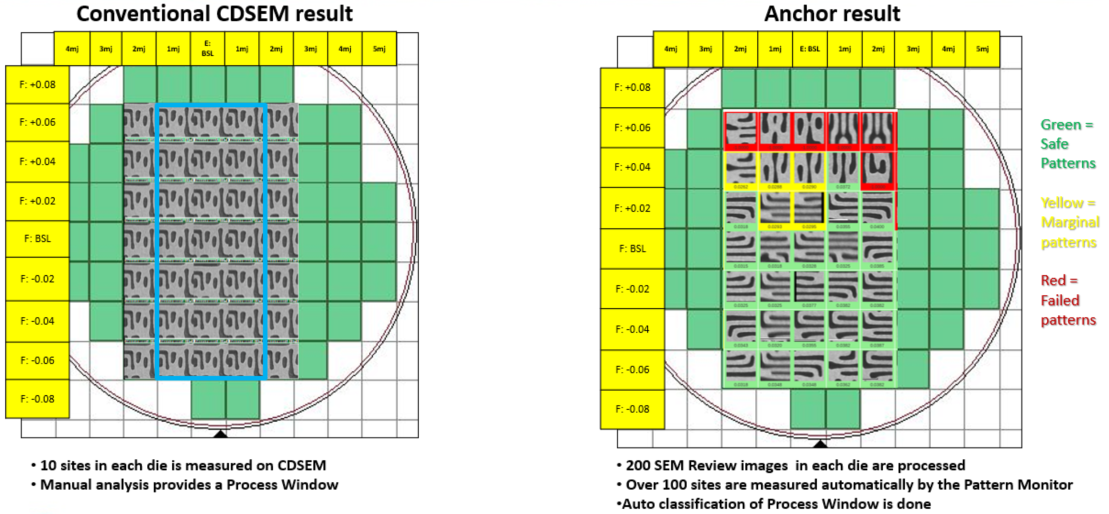

Figure 16.

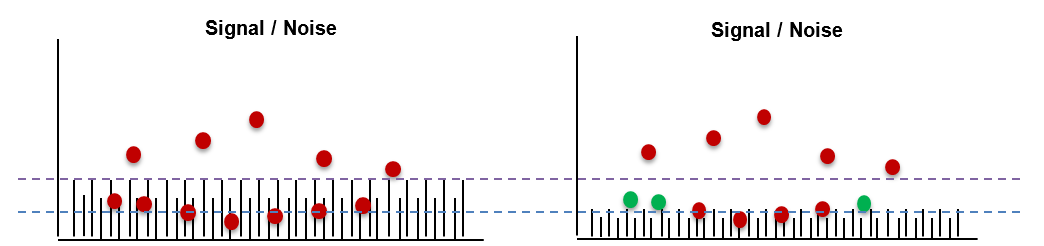

Conventional vs Anchor FEM Analysis [12]. The conventional method of analyzing Focus/Exposure Modulations (FEM) is by performing a high-sensitivity wafer inspection followed by a large SEM Review in which tens of thousands of SEM images are captured and analyzed for the presence of

hard defects. The conventional method does not take

pattern fidelity into account and therefore cannot track or report the subtle deviations that occur on each pattern across each modulation. Subtle deviations – pattern

fidelity variations – are playing an increasingly significant role in parametric yield loss. Establishing a lithography process window that takes into account pattern fidelity (not just pattern defectivity) leads to a more robust result

[12,13,14,15]. A side-by-side comparison of the process window map obtained by conventional method and by Anchor’s method is shown in

Figure 16. Anchor’s computational system redefines and reinvents FEM/PWQ analysis in the following ways:

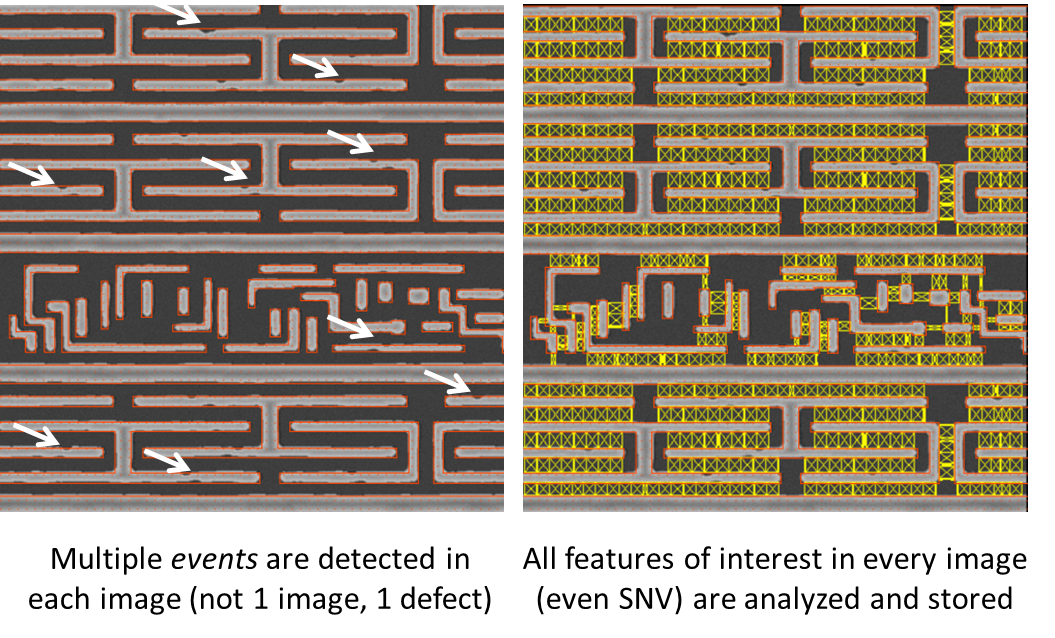

The computational system checks every SEM image for the presence of die-to-database defects. Some of these defects are not detectable using conventional die-to-die or die-to-golden die techniques. Multiple defects can be detected on a single image.

The computational system measures every feature of interest in every SEM image (massive metrology) to generate pattern uniformity statistics for each pattern of interest. This enables pattern fidelity analysis.

The computational system tracks the uniformity of like patterns across each modulation to generate Bossung Curves automatically for hundreds or thousands or tens of thousands of patterns. These Bossung Curves supplement – not replace – conventional CD-SEM analysis because accuracy of measurements from Review SEM is limited. Nevertheless, these Bossung Curves are produced more quickly and cover a significantly wider set of patterns. They provide valuable early feedback.

The combination of (a) better defect detection, (b) pattern uniformity/fidelity analysis, and (c) generation of Bossung Curves for a wide set of patterns results in the reinvention of PWQ/FEM analysis.