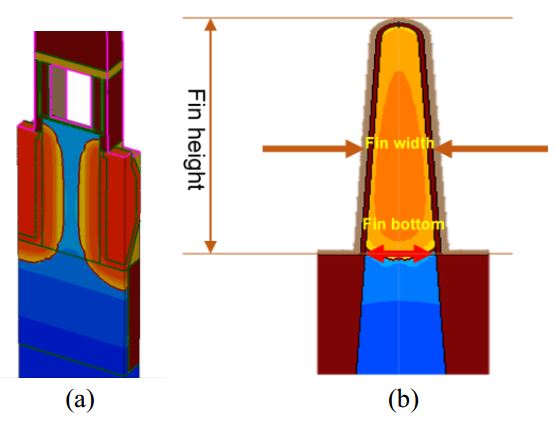

FinFET structure has advanced the MOSFETs due to raised channel and multi-gate control which introduce more effective channel width and the stronger gate control. Since the electrical current mainly flow along the fin, therefore, the fin height can directly influence the drive current of the device. Since the taller fin gives wider effective channel width, the effective channel width can be written,

(1)

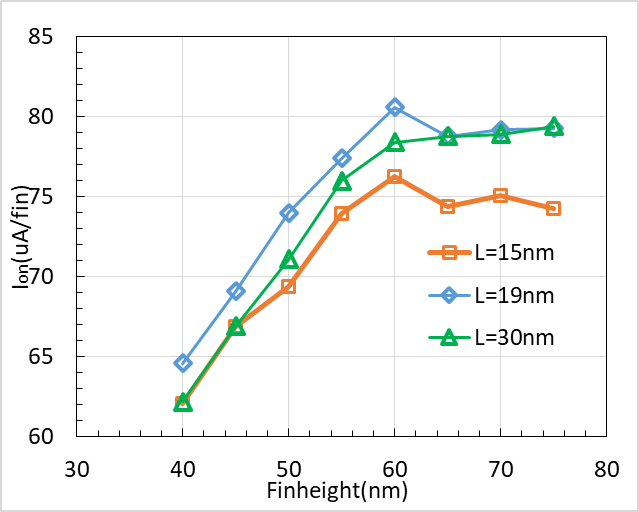

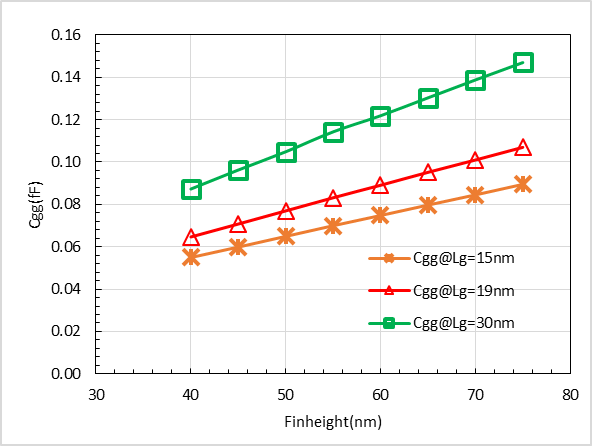

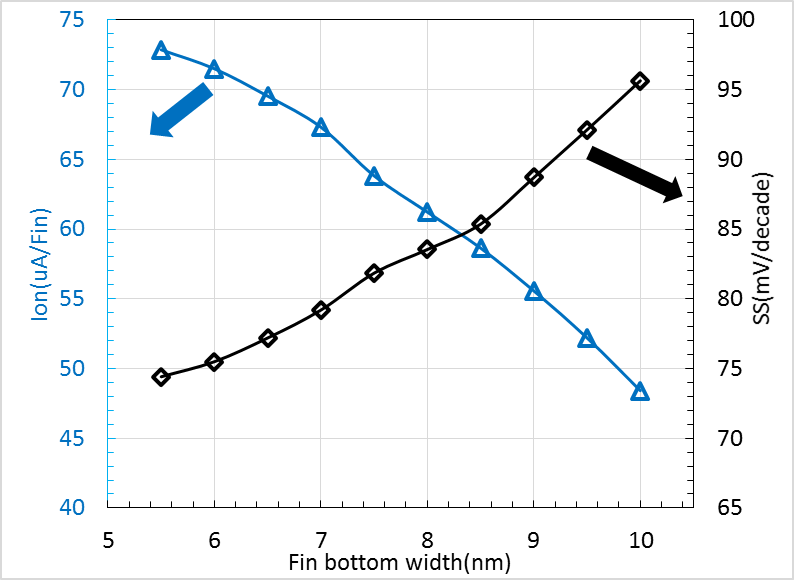

where the H_fin represents fin height and W_fin is width of the fin. Then, more carrier flow along the channel. However, because of the narrow critical dimension of 5 nm FinFET structure, the parasitic capacitance of the device is to a large extent subjected to narrow spacer and extreme thin oxide thickness. Figure 2 shows that the drive current Ion of device increases linearly as the fin height increases from 40 nm to 60 nm, about 22.9%, 24.8%, and 26.1% boost for 15 nm, 19 nm and 30 nm gate length device, respectively. As the fin height reaches over 60 nm, the drive current approaches a saturation value since the source/drain height does not change.

Figure 2.

FinFET device drive current boost as the fin height increase. Figure 3.

Linear increase of the device capacitance Cgg as the fin height increase. At the same time, the capacitance of device Cgg exhibits a linear rise as the fin height grows from 40 nm to 75 nm. The capacitance is not affected by source/drain height mainly because the capacitance of gate to fin is the main contributor to Cgg . The increase of fin height from 40 nm to 60 nm has introduced 37.7%, 36%, and 39.6% rise in Cgg for 15 nm, 19 nm, and 30 nm gate lengths, respectively. Compared to drive current increase versus fin height, the increase of Cgg is more rapid. However, in manufacturing process, to make a tall fin while keeping the pitch fixed needs challenging high aspect ratio etch and film deposition technologies. As a more advanced technology node over 16/14 nm and 7 nm, the goal for the 5 nm drive current is defined as 70 A/fin. Therefore, we set the optimized fin height between 50 nm to 60 nm, maintaining the drive current goal while the Cgg is not too large.

4. Threshold Voltage Shift by Quantum Confinement Effect

As the fin width shrinks to several nanometers, the dimension confinement causes sub-band splitting due to the Quantum Mechanical (QM) effect. Given a certain gate voltage bias, as it has been reported that the inversion charge density resulted by the sub-band splitting is smaller than the classical (CL) one [6,7], the QM channel potential is lower than the CL one, inducing the Vth shift. The quantum confinement effect caused Vth shift can be described by,

(2)

where the SS represents the subthreshold swing, q is carrier charge, and the represents the difference of channel potential between QM and CL model.

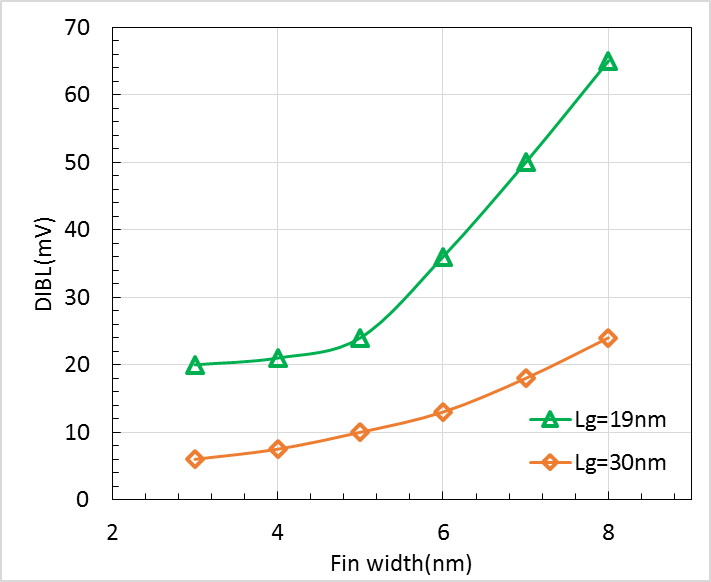

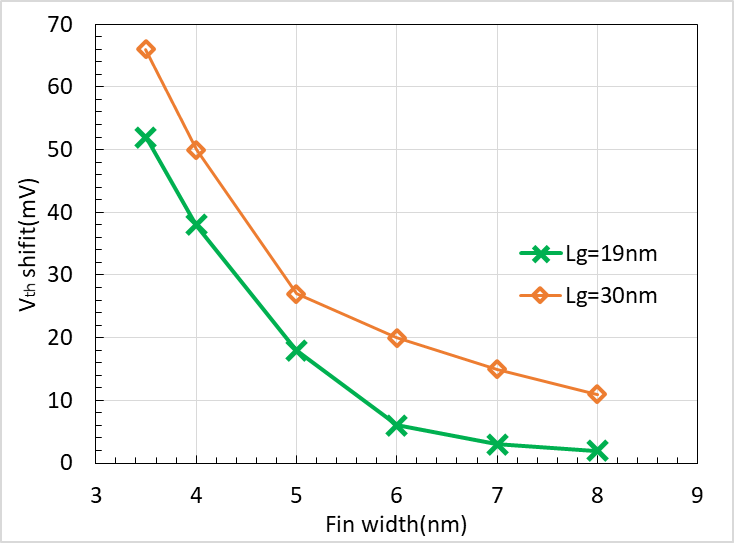

Figure 4.

FinFET device DIBL performance as fin width shrinking. Little DIBL due to gate control. Figure 5.

Simulation results of threshold voltage shift by quantum confinement effect. The simulation results are shown in Figure 4 and Figure 5. It indicates that, though the device DIBL can benefit from fin width shrink, the Vth shift will become worse by quantum confinement effect. When fin width is large enough, 6 nm for example, the Vth shift is not significant. But, when the fin narrows to 5 nm the Vth shift can be significant, which exhibits a steep Vth increase as the fin continues to shrink, especially when the fin narrows to 4 nm, the \({V}_{th}\) shift can reach 50 mV (19 nm gate length device). Therefore, it is reasonable to keep the fin width at 5 nm or greater.